LSIデザインサービス

高速伝送開発

高速伝送技術概要

通信されるデータ量は増加しつつあります。基幹系や都市間の長距離通信をはじめとしたEthernet等の有線通信分野はもちろん、HDMIに代表される民生機器向けインターフェイスの分野でもデータ伝送の高速化が図られています。

また、5Gなどの高速通信が発展することで、センサーおよびその周辺機器間のデータ通信も増え、用途に合わせた様々な通信規格が高速化しています。

TOPPANは、このような技術動向に対応した

・撮像素子向けトランスミッタ (MIPI D-PHY)

・FPD用LVDS/RSDSトランスミッタ

・モバイル通信用sub-LVDSトランスミッタ

・プロジェクタ用レシーバ

などの開発実績があります。

今後、さらなる高速化と、多様化する高速通信インターフェイスの開発・実現を目指しています。

また、5Gなどの高速通信が発展することで、センサーおよびその周辺機器間のデータ通信も増え、用途に合わせた様々な通信規格が高速化しています。

TOPPANは、このような技術動向に対応した

・撮像素子向けトランスミッタ (MIPI D-PHY)

・FPD用LVDS/RSDSトランスミッタ

・モバイル通信用sub-LVDSトランスミッタ

・プロジェクタ用レシーバ

などの開発実績があります。

今後、さらなる高速化と、多様化する高速通信インターフェイスの開発・実現を目指しています。

開発事例

| 開発事例 | 特徴/仕様 |

|---|---|

|

FPD用LVDS Transmitter |

転送レート: 3.78Gbps(4channel) |

|

プロジェクターのRGB制御 |

転送レート: 1.2Gbps/channel |

|

CIS用 MIPI DPHY送信回路 |

転送レート: ~2Gbps/channel |

|

高速データ通信用PLL IP |

回路形式:Integer PLL、LC VCO VCO |

|

フラクショナルPLL IP |

分周設定: 整数部8bit、小数部20bit |

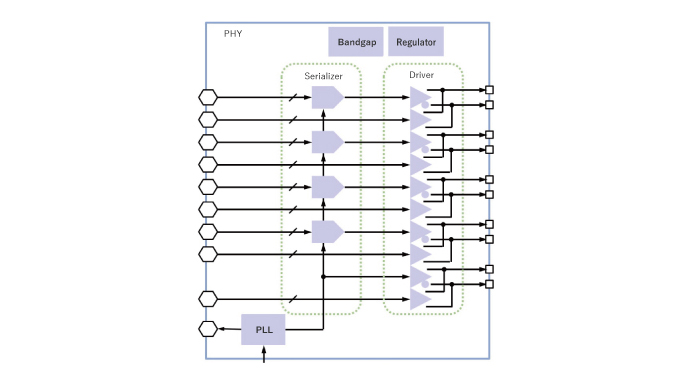

■個体撮像素子向けMIPI D-PHY

【特徴】

(トランスミッタ)

・MIPI D-PHY規格に準拠したPHYブロック

・データ4Lane とクロック 1Lane 構成

・PLL内蔵

・プロセス電圧に応じたReguratorの設計

・PAD接続部のESD/Latch up対策

・電源1.5V (1.2V)

・0.15um CMOSプロセス (55nm,40nm CMOSプロセス)

【ブロック図】